#### **Data Communications**

# Quad Universal Asynchronous Receiver/Transmitter (UART) with FIFO's

### Description

The IMP16C554 is a universal asynchronous receiver and transmitter with 16 byte transmit and receive FIFO. A programmable baud rate generator is provided to select transmit and receive clock rates from 50Hz to 1.5MHz.

The IMP16C554 is an improved version of the IMP16C550 UART with higher operating speed and lower access time. The IMP16C554 on board status registers provides the error conditions, type and status of the transfer operation being performed. Included is complete MODEM control capability, and a processor interrupt system that may be software tailored to the user's requirements. The IMP16C554 provides internal loop-back capability for on board diagnostic testing.

The IMP16C554 is fabricated in an advanced 1.2u CMOS process to achieve low drain power and high speed requirements.

## Key Features

- 16 byte receive FIFO with error flags

- Modem control signal (CTS\*, RTS\*, DSR\*, DTR\*, RI\* ,CD\*)

- Programmable character lengths(5,6,7,8)

- Even, odd, or no parity bit generation and detection

- Status report register

- Independent transmit and receive control

- TLL compatible inputs. outputs

- Software compatible with Ei8250, 1Ei16C550

- 460.8kHz transmit/receive operation with 7.372

MHz crystal or external clock source

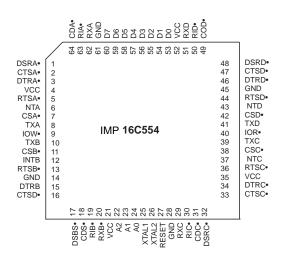

68-PIN PLCC

#### **64-PIN QFP**

# *IMP16C554*

| symbol           | pin            | Signal Type | Pin Description                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D0-D7            | 5-66           | I/O         | Bi-directional data bus. Eight bit, three state data bus to<br>transfer information to or from the CPU. Do is the least<br>significant bit of the data bus and the first serial data bit to be<br>received or transmitted.                                                                              |  |  |  |  |

| RX A-B<br>RX C-D |                |             | Serial data input. The serial information (data) received from<br>serial port to IMP16C554 receive input circuit . A mark (high<br>is logic one and a space (low)is logic zero. During the local<br>loopback mode the RX input is disabled from external<br>connection and to the TX output internally. |  |  |  |  |

| TX A-B<br>TX C-D | 17.19<br>51.53 | ο           | Serial data output. The serial data is transmitted via this pin<br>with additional start, stop and parity bits. The TX will be held<br>in mark(high) state during reset, local loopback mode o<br>when the transmitter is disabled.                                                                     |  |  |  |  |

| CS*A-B<br>CS*C-D | 16.20<br>50.54 | I           | Chip select. (active low) A low at this pin enables the IMP16C554/CPU data transfer operation. Each UART section of the IMP16C554 can be accessed independently.                                                                                                                                        |  |  |  |  |

| XTAL1            | 35             | I           | Crystal input 1 or external clock input. A crystal can be<br>connected to this pin and XTAL2 pin to utilize the interna<br>oscillator circuit. An external clock can be used to clock<br>internal circuit and baud rate generator for custon<br>transmission rates.                                     |  |  |  |  |

| XTAL2            | 36             | 0           | Crystal input 2 or buffered clock output. See XTAL1.                                                                                                                                                                                                                                                    |  |  |  |  |

| LOW*             | 18             | I           | Write strobe.(active low)A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                                                                                                    |  |  |  |  |

| GND<br>GND       | 6.23<br>40.57  | О           | Signal and power ground.                                                                                                                                                                                                                                                                                |  |  |  |  |

| IOR*             | 52             | I           | Read strobe.(active low)A low level on this pin transfers the contents of the IMP16C554 data bus to the CPU.                                                                                                                                                                                            |  |  |  |  |

#### SYMBOL DESCRIPTION

| symbol             | pin            | Signal<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TXRDY*             | 39             | 0              | Transmit ready. (active low) This pin goes high when the transmit FIFO of the IMP16C554 is full. It can be used as a single or multi-transfer.                                                                                                                                                                                     |  |  |  |

| A2                 | 32             | I              | Address select line 2.To select internal registers.                                                                                                                                                                                                                                                                                |  |  |  |

| A1                 | 33             | 1              | Address select line 1.To select internal registers.                                                                                                                                                                                                                                                                                |  |  |  |

| A0                 | 34             | I              | Address select line 0. To select internal registers.                                                                                                                                                                                                                                                                               |  |  |  |

| RXRDY*             | 38             | 0              | Receive ready.(active low ) This pin goes low when the receive FIFO is full. It can be used as a single or multi-transfer.                                                                                                                                                                                                         |  |  |  |

| INTSEL             | 65             | I              | Interrupt type select. Enable /disable the interrupt three state function. Normal interrupt output can be selected by connecting this pin to VCC(MCR bit-3 does not have any effect on the interrupt output ).The three state interrupt output is selected when this pin is left open or connected to GND and MCR bit-3 is to "1". |  |  |  |

| INT A-B<br>INT C-D | 15.21<br>49.55 | 0              | Interrupt output.( active high) this pin goes high (when enable<br>by the interrupt enable register)whenever a receiver error.<br>receiver data available. transmitter empty, or modem status<br>condition flag is detected.                                                                                                       |  |  |  |

| RTS*A-B<br>RTS*C-D | 14.22<br>48.56 | 0              | Request to send.(active low) To indicate that the transmitter<br>has data ready to send .Writing a "1" in the modem control<br>register(MCR bit-1) will set this pin to a low state. After the<br>reset this pin will be set to high. Note that this pin does not<br>have any effect on the transmit or receive operation.         |  |  |  |

| DTR*A-B<br>DTR*C-D | 12.24<br>46.58 | 0              | Data terminal ready. (active low) To indicate that IMP16C554 is ready to receive data. This pin can be controlled via the modem control register (MCR bit-0).writing a "1" at the MCR bit-0 will set the DTR* output to low.                                                                                                       |  |  |  |

#### SYMBOL DESCRIPTION

| symbol             | pin            | Signal Type | Pin Description                                                                                                                                                                                 |

|--------------------|----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                |             | This pin will be set to high state after writing a "0" to that register or after the reset. Note that this pin does not have any effect on the transmit or receive operation.                   |

| RESET              | 37             | I           | Master reset.(active high)A high on this pin will reset all<br>the outputs and internal registers. The transmitter<br>output and the receiver input will be disabled during<br>reset time.      |

| CTS*A-B<br>CTS*C-D | 11.25<br>45.59 | I           | Clear to send. (active low) The CTS* signal is a MODEM control function input whose conditions can be tested by reading the MSR BIT-4. CTS* has no effect on the transmit or receive operation. |

| DSR*A-B<br>DSR*C-D | 10.26<br>44.60 | Ι           | Data set ready. ( active low) A low on this pin indicates<br>the MODEM is ready to exchange data with UART. This<br>pin does not have any effect on the transmit or receive<br>operation.       |

| CD*A-B<br>CD*C-D   | 9.27<br>43.61  | I           | Carrier detect.(active low) A low on this pin indicates the carrier has been detected by the modem.                                                                                             |

| RI*A-B<br>RI*C-D   | 8.28<br>42.62  | I           | Ring detect indicator. ( active low) A low on this pin indicates the modem has received a ringing signal from telephone line.                                                                   |

| VCC<br>VCC         | 13.30<br>47.64 | I           | Power supply input.                                                                                                                                                                             |

## IMP16C554 ACCESSIBLE REGISTERS

| Aź | 2A1 | A0 | Registe<br>r | BIT-7                                | BIT-6                            | BIT-5                             | BIT-4                  | BIT-3                            | BIT-2                                       | BIT-1                               | BIT-0                          |

|----|-----|----|--------------|--------------------------------------|----------------------------------|-----------------------------------|------------------------|----------------------------------|---------------------------------------------|-------------------------------------|--------------------------------|

| 0  | 0   | 0  | RHR          | bit-7                                | bit-6                            | bit-5                             | bit-4                  | bit-3                            | bit-2                                       | bit-1                               | bit-0                          |

| 0  | 0   | 0  | THR          | bit-7                                | bit-6                            | bit-5                             | bit-4                  | bit-3                            | bit-2                                       | bit-1                               | bit-0                          |

| 0  | 0   | 1  | IER          | 0                                    | 0                                | 0                                 | 0                      | Modem<br>status<br>interrup<br>t | Receiv<br>e line<br>status<br>interru<br>pt | Transmi<br>t<br>holding<br>register | Receive<br>holding<br>register |

| 0  | 1   | 0  | FCR          | RCV<br>R<br>trigge<br>r<br>(MSB<br>) | RCV<br>R<br>trigge<br>r<br>(LSB) | 0                                 | 0                      | DMA<br>Mode<br>select            | XMITF<br>IFO<br>reset                       | RCVRF<br>IFO<br>reset               | FIFO<br>enable                 |

| 0  | 1   | 0  | ISR          | 0/FIF<br>Os<br>enabl<br>ed           | 0/FIF<br>Os<br>enabl<br>ed       | 0                                 | 0                      | int<br>priority<br>bit-2         | Int<br>priority<br>bit-1                    | Int<br>priority<br>bit-0            | Int<br>status                  |

| 0  | 1   | 1  | LCR          | Divis<br>or<br>latch<br>enabl<br>e   | Set<br>break                     | Set<br>parity                     | Even<br>parity         | Parity<br>enable                 | Stop<br>bits                                | Word<br>length<br>bit-1             | Word<br>length<br>bit-0        |

| 1  | 0   | 0  | MCR          | 0                                    | 0                                | 0                                 | Loop<br>back           | INT<br>enable                    | Not<br>used                                 | RTS*                                | DTR*                           |

| 1  | 0   | 1  | LSR          | o/FIF<br>O<br>error                  | trans<br>empt<br>y               | trans<br>holdi<br>ng<br>empt<br>y | break<br>interr<br>upt | framing<br>error                 | parity<br>error                             | overrun<br>error                    | receive<br>data<br>ready       |

| 1  | 1   | 0  | MSR          | CD                                   | RI                               | DSR                               | CTS                    | delta<br>CD*                     | delta<br>RI*                                | delta<br>DSR*                       | delta<br>CTS*                  |

| 1  | 1   | 1  | SPR          | bit-7                                | bit-6                            | bit-5                             | bit-4                  | bit-3                            | bit-2                                       | bit-1                               | bit-0                          |

| 0  | 0   | 0  | DLL          | bit-7                                | bit-6                            | bit-5                             | bit-4                  | bit-3                            | bit-2                                       | bit-1                               | bit-0                          |

| 0  | 0   | 1  | DLM          | bit-15                               | bit-14                           | bit-13                            | bit-12                 | bit-11                           | bit-10                                      | bit-9                               | bit-8                          |

DLL and DLM are accessible only when LCR bit-7 is set to "1".

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如 要下载或阅读全文,请访问: <u>https://d.book118.com/25604121413</u> 0010150