PACKAGE OUTLINE

15

### 26 W BTL and 2 $\times$ 13 W SE or $4 \times 13$ W SE power amplifier

### CONTENTS

| 1                                                    | FEATURES                                                                                                                                                                                       | 16                                     | SOLDERING                                                                                                                                                                                                  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                    | APPLICATIONS                                                                                                                                                                                   | 16.1                                   | Introduction to soldering through-hole mount                                                                                                                                                               |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>8.1<br>8.2<br>8.3 | GENERAL DESCRIPTION<br>QUICK REFERENCE DATA<br>ORDERING INFORMATION<br>BLOCK DIAGRAM<br>PINNING<br>FUNCTIONAL DESCRIPTION<br>Mode select switch<br>Mode select<br>Built-in protection circuits | 16.2<br>16.3<br>16.4<br>17<br>18<br>19 | packages<br>Soldering by dipping r by sold wave<br>Manual solde ng<br>Suitability of thro gh-hole nt IC packages<br>for dipping and wave oldering methods<br>DATA SHEE TATUS<br>DEFINITIONS<br>DISCLAIME S |

| 8.4                                                  | Short-circuit protection                                                                                                                                                                       |                                        |                                                                                                                                                                                                            |

| 9                                                    | LIMITING VALUES                                                                                                                                                                                |                                        |                                                                                                                                                                                                            |

| 10                                                   | HANDLING                                                                                                                                                                                       |                                        |                                                                                                                                                                                                            |

| 11                                                   | THERMAL CHARACTERISTICS                                                                                                                                                                        |                                        |                                                                                                                                                                                                            |

| 12                                                   | DC CHARACTERISTICS                                                                                                                                                                             |                                        |                                                                                                                                                                                                            |

| 13                                                   | AC CHARACTERISTICS                                                                                                                                                                             |                                        |                                                                                                                                                                                                            |

| 14                                                   | APPLICATION INFORMATION                                                                                                                                                                        |                                        |                                                                                                                                                                                                            |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5                 | Input configuration<br>Output power<br>Power dissipation<br>Supply Voltage Ripple Rejection (SVRR)<br>Switch-on and switch-off                                                                 |                                        |                                                                                                                                                                                                            |

- 14.5 Switch-on and switch-off

- 14.6 PCB layout and grounding

- 14.7 Typical performance characteris ics

### **TDA8512J**

TDA8512J

# 26 W BTL and 2 $\times$ 13 W SE or 4 $\times$ 13 W SE power amplifier

### **1 FEATURES**

- Requires very few external components

- High output power

- Low output offset voltage Bridge-Tied Load (BTL) channel

- Fixed gain

- Good ripple rejection

- · Mode select switch: operating, mute and standby

- Short-circuit safe to ground and across load

- · Low power dissipation in any short-circuit condition

- Thermally protected

- Reverse polarity safe

- Electrostatic discharge protection

- No switch-on and switch-off plops

- Flexible leads

- · Low thermal resistance

- Identical inputs: inverting and non-inverting.

### 2 APPLICATIONS

- Multimedia systems

- Active speaker systems (stere with sub woofer or QUAD).

#### **3 GENERAL DESCR PTION**

The TDA8512J is an tegrated class-B output amplifier in a 17-lead Single-In-Line SIL) power package. It contains  $4 \times 13$  W Single Ended (SE) amplifiers of which two can be used to con gure a 26 W BTL amplifier.

### 4 QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                       | ONDIT ONS                      | MIN. | TYP. | MAX.  | UNIT |

|---------------------|---------------------------------|--------------------------------|------|------|-------|------|

| General             |                                 |                                |      | 1    |       | 1    |

| V <sub>P</sub>      | supply voltage                  |                                | 6    | 15   | 18    | V    |

| I <sub>ORM</sub>    | repetitive peak output current  |                                | _    | -    | 4     | A    |

| I <sub>q(tot)</sub> | total quiescent current         |                                | _    | 80   |       | mA   |

| I <sub>stb</sub>    | standby current                 |                                | _    | 0.1  | 100.0 | μA   |

| BTL channel         |                                 | ·                              |      |      | •     |      |

| Po                  | output power                    | $R_{L} = 4 \Omega$ ; THD = 10% | -    | 26   | _     | W    |

| SVRR                | supply voltage ripple rejecti n |                                | 46   | -    | -     | dB   |

| V <sub>n(o)</sub>   | noise output voltage            | R <sub>s</sub> = 0 Ω           | _    | 70   | -     | μV   |

| Z <sub>i</sub>      | input impedance                 |                                | 25   | -    | -     | kΩ   |

| $ \Delta V_{OO} $   | DC output offse voltage         |                                | -    | -    | 150   | mV   |

| SE channels         |                                 | •                              |      |      | •     |      |

| Po                  | output power                    | THD = 10%                      |      |      |       |      |

|                     |                                 | $R_L = 4 \Omega$               | _    | 7.0  | -     | W    |

|                     |                                 | $R_L = 2 \Omega$               | _    | 13.0 | _     | w    |

| SVRR                | s ly vo age ripple rejection    |                                | 46   | -    | -     | dB   |

| V <sub>n(o)</sub>   | nois outpu voltage              | R <sub>s</sub> = 0 Ω           | -    | 50   | -     | μV   |

| Z <sub>i</sub>      | input impedance                 |                                | 50   | -    | -     | kΩ   |

#### 5 ORDERING INFORMATION

| TYPE     |        | PACKAGE                                                          |          |  |  |

|----------|--------|------------------------------------------------------------------|----------|--|--|

| NUMBER   | NAME   | DESCRIPTION                                                      | VERSION  |  |  |

| TDA8512J | DBS17P | plastic DIL-bent-SIL power package; 17 leads (lead length 12 mm) | SOT243-1 |  |  |

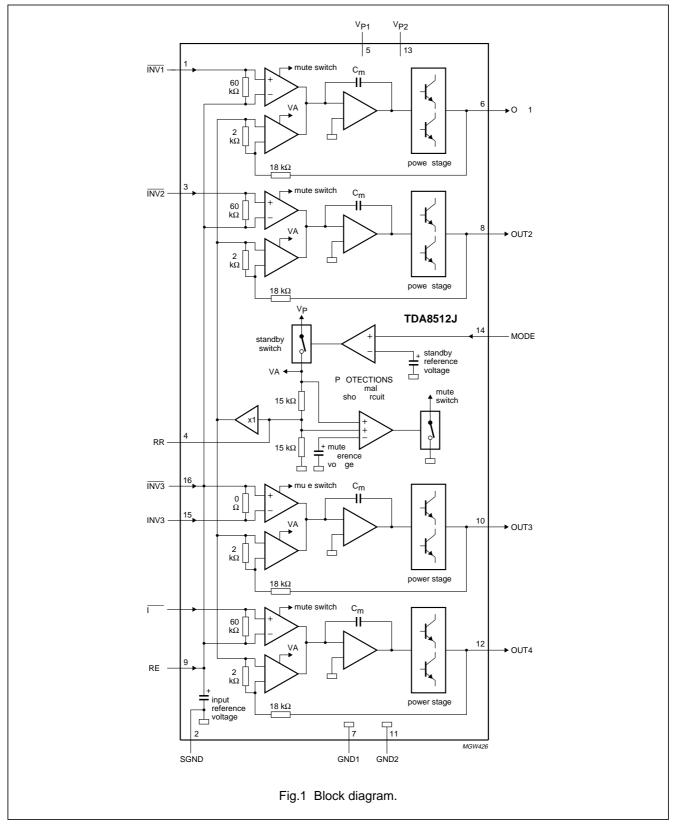

### 6 BLOCK DIAGRAM

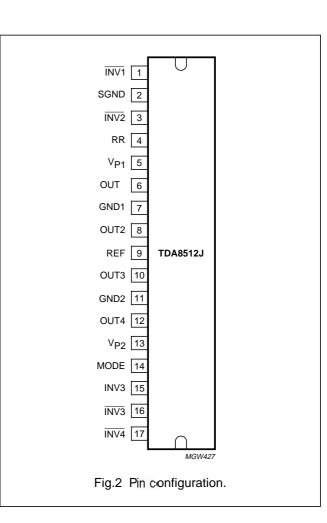

### 7 PINNING

| SYMBOL          | PIN | DESCRIPTION                     |

|-----------------|-----|---------------------------------|

| ĪNV1            | 1   | non-inverting input 1           |

| SGND            | 2   | signal ground                   |

| ĪNV2            | 3   | non-inverting input 2           |

| RR              | 4   | supply voltage ripple rejection |

| V <sub>P1</sub> | 5   | supply voltage 1                |

| OUT1            | 6   | output 1                        |

| GND1            | 7   | power ground 1                  |

| OUT2            | 8   | output 2                        |

| REF             | 9   | reference voltage input         |

| OUT3            | 10  | output 3                        |

| GND2            | 11  | power ground 2                  |

| OUT4            | 12  | output 4                        |

| V <sub>P2</sub> | 13  | supply voltage 2                |

| MODE            | 14  | mode select switch input        |

| INV3            | 15  | inverting input 3               |

| ĪNV3            | 16  | non-inverting input 3           |

| ĪNV4            | 17  | non-inverting input 4           |

TDA8512J

## 26 W BTL and $2 \times 13$ W SE or $4 \times 13$ W SE power amplifier

### 8 FUNCTIONAL DESCRIPTION

The TDA8512J contains four identical amplifiers and can be used in the configurations:

- Two SE channels (fixed gain 20 dB) and one BTL channel (fixed gain 26 dB)

- Four SE channels.

( $R_L$  depends on the application).

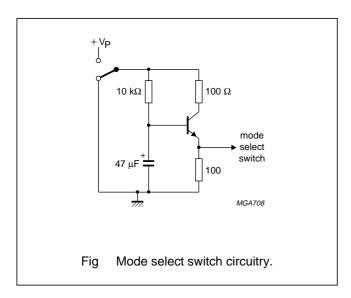

### 8.1 Mode select switch

A special feature of the TDA8512J device is the mode select switch (pin MODE), offering:

- Low standby current (<100 μA)

- Low switching current (low cost supply switch)

- Mute facility.

To avoid switch-on plops, it is advised to keep the amplifier in the mute mode for longer than 100 ms to allow charging of the input capacitors at pins  $\overline{INV1}$ ,  $\overline{INV2}$ ,  $\overline{INV3}$ ,  $\overline{INV3}$ and  $\overline{INV4}$ . This can be achieved by:

- · Control via a microcontroller

- An external timing circuit (see Fig.3).

The circuit slowly ramps up the voltage at the pin MODE when switching on, and results in fast muting when switching off.

#### 8.2 Mode select

For the 3 functional modes; standby, mute and operate, the pin MODE can be driven by a 3-stae logic output stage: e.g. microcontroller with som ex components for DC level shifting. (see Fig 10).

Standby mode will be act ated by applying a low DC level between 0 and 2 V. The power consumption of the device will be reduced to less han 1.5 mW. The input and output pins are floa ng high impedance condition.

Mute mode will be a t vated by a applying a DC level between 3.3 and 6.4 V. e outputs of the amplifier will be muted (no audio ou ut); ho ever, the amplifier is DC biased and the DC vel of the input and output pins stays on half the supply voltage.

Operating mode is obtained at a DC level between 8.5 V and  $\mathsf{V}_\mathsf{P}$

### 8.3 Built-in protection circuits

T devic contains both a thermal protection, and a sho t-circu protection.

Th m I protection:

The junction temperature is measured by a temperature s sor; at a junction temperature of about 160 °C this d tection circuit switches off the power stages.

Short-circuit protection (outputs to ground, supply and across the load):

Short-circuit is detected by a so called Maximum Current Detection circuit, which measures the current in the positive, respectively negative supply line of each power stage. At currents exceeding (typical) 6 A, the power stages are switched off during some ms.

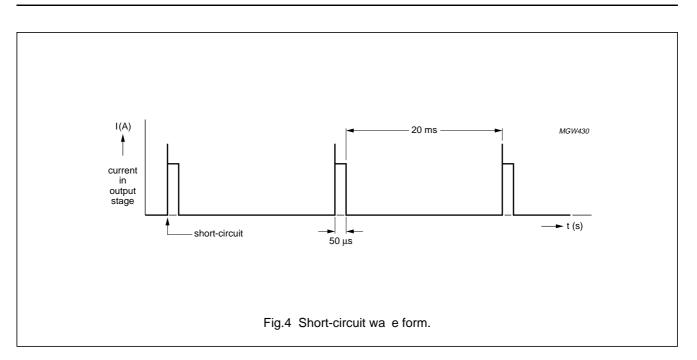

### 8.4 Short-circuit protection

When a short-circuit during operation to either GND or across the load of one or more channels occurs, the output stages are switched off for approximaely 20 ms. After that time, it is checked during approximately 50  $\mu$ s to see whether the short-circuit is still present. Due to this duty factor of 50  $\mu$ s per 20 ms, the average supply current is very low during this short-circuit (approximately 40 mA, see Fig.4).

### TDA8512J

### 9 LIMITING VALUES

In accordance with the Absolute Maximum Rating Sy em (IE 601 4).

| SYMBOL           | PARAMETER                          | CONDITIONS        | MIN. | MAX. | UNIT |

|------------------|------------------------------------|-------------------|------|------|------|

| V <sub>P</sub>   | supply voltage                     | opera ing         | -    | 18   | V    |

|                  |                                    | o signal          | -    | 21   | V    |

| I <sub>OSM</sub> | non-repetitive peak output current |                   | -    | 6    | A    |

| I <sub>ORM</sub> | repetitive peak output current     |                   | -    | 4    | A    |

| V <sub>sc</sub>  | short-circuit safe voltage         | op rating; note 1 | -    | 18   | V    |

| V <sub>rp</sub>  | reverse polarity volta             |                   | -    | 6    | V    |

| P <sub>tot</sub> | total power dissipation            |                   | -    | 60   | W    |

| T <sub>stg</sub> | storage temperatur                 |                   | -55  | +150 | °C   |

| T <sub>amb</sub> | ambient tempera ure                |                   | -40  | +85  | °C   |

| T <sub>vj</sub>  | virtual junc temperature           |                   | -    | 150  | °C   |

Note

1. To ground and acro s load.

### 10 HANDLING

ESD protection o his d vice complies with the Philips' General Quality Specification (GQS).

### TDA8512J

### **11 THERMAL CHARACTERISTICS**

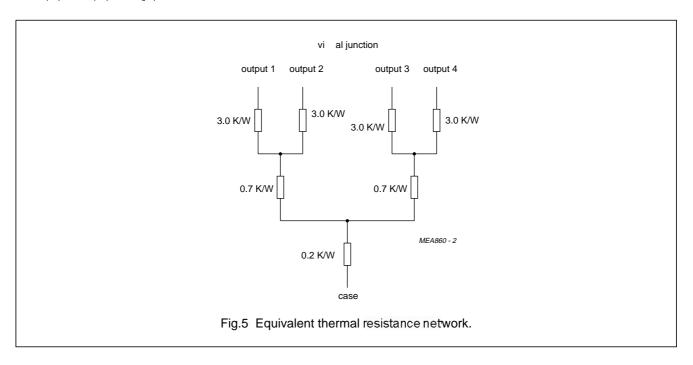

In accordance with IEC 60747-1.

| SYMBOL               | PARAMETER                                   | CONDITIONS | VALUE | UNIT |

|----------------------|---------------------------------------------|------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in ree air | 40.0  | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    | see Fig.5  | 1.3   | K/W  |

The measured thermal esistance of the IC-package ( $R_{th(j-c)}$ ) is maximum 1.3 K/W if all four ch nnels are driven. For a naximum ambient temperature of 60 °C and  $V_P = 15$  V, the following calculation for th eatsink an be made:

For the application two SE outputs with 2  $\Omega$  load, the measured worst-case sine-wave dissipa on is 2  $\times$  7 W

For the application BTL output with 4  $\Omega$  load, the worst-case sine-wave dissipation is 1 5 W.

So the total power dissipation is  $P_{d(tot)} = 2 \times 7 + 12.5 \text{ W} = 26.5 \text{ W}.$

At  $T_{j(max)}$  = 150 °C the temperature increase, caused by the power dissipation, is:  $\Delta T$  = 150 °C - 60 °C = 90 °C.

So  $P_{d(tot)} \times R_{h(tot)} = \Delta T = 90$  K. As a result:  $R_{th(tot)} = \frac{90}{26.5} = 3.4$  K/W hich means:

$R_{th(hs)} = R_{th(tot)} - R_{h(j-c)} = 3.4 - 1.3 = 2.1 \text{ K/W}.$

The above calculation is for application at worst-case (stereo) sine-wa output signals. In practice, music signals will be applied. In that case the maximum power dissipation will be abot the has the sine-wave power dissipation, which allows the use of a smaller heatsink.

So  $P_{d(tot)} \times R_{h(tot)} = \Delta T = 90$  K. As a result:  $R_{th(tot)} = \frac{90}{13 \cdot 5} = 6.8$  K/W which means:

$R_{th(hs)} = R_{th(tot)} - R_{h(j-c)} = 6.8 - 1.3 = 5.5 \text{ K/W}.$

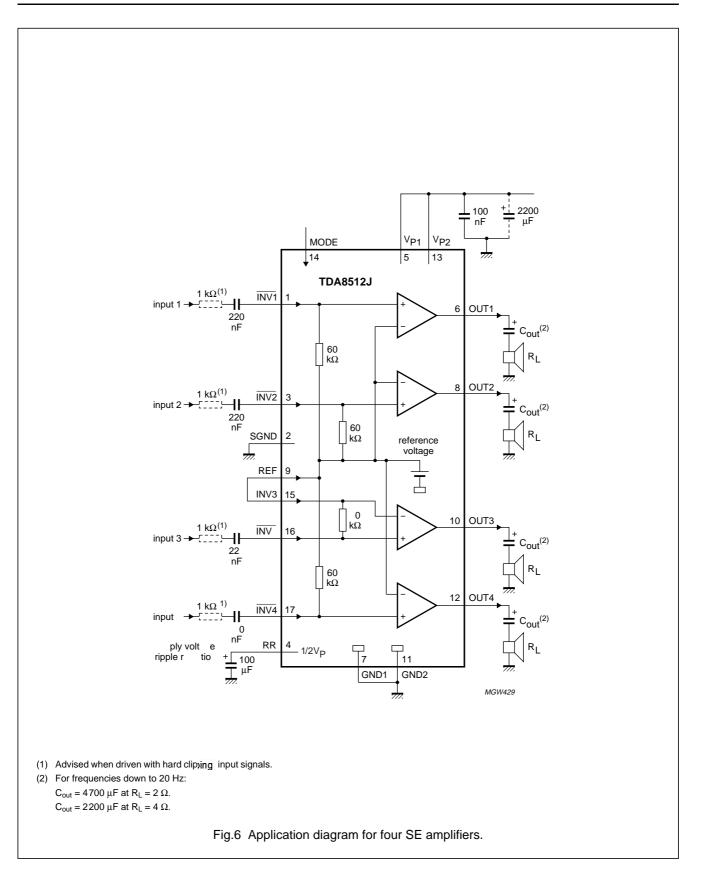

### 12 DC CHARACTERISTICS

$V_P$  = 15 V;  $T_{amb}$  = 25 °C; measured according to Figs 6 and 7; unless otherwise specified.

| SYMBOL              | PARAMETER                | CONDITIONS                                       | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------------------------|--------------------------------------------------|------|------|------|------|

| Supply              |                          |                                                  |      | 4    | -1   |      |

| V <sub>P</sub>      | supply voltage           | note 1                                           | 6    | 15   | 18   | V    |

| I <sub>q(tot)</sub> | total quiescent current  |                                                  | _    | 0    | 0    | mA   |

| Vo                  | DC output voltage        |                                                  | _    | 6.9  | -    | V    |

| $ \Delta V_{OO} $   | DC output offset voltage | note 2                                           | -    |      | 150  | mV   |

| Mode selec          | t switch                 |                                                  |      |      | I.   |      |

| V <sub>sw(on)</sub> | switch-on voltage        |                                                  | 5    | _    | _    | V    |

| Mute condi          | tion                     |                                                  |      |      |      |      |

| V                   | mute voltage             |                                                  | 3.3  | -    | 6.4  | V    |

| Vo                  | output voltage           | V <sub>i(max)</sub> = 1 V; f <sub>i</sub> = 1 kH | _    | -    | 2    | mV   |

| $ \Delta V_{OO} $   | DC output offset voltage | note 2                                           |      | -    | 150  | mV   |

| Standby co          | ndition                  |                                                  |      |      |      |      |

| V <sub>stb</sub>    | standby voltage          |                                                  | 0    | _    | 2    | V    |

| I <sub>stb</sub>    | standby current          |                                                  | _    | -    | 100  | μA   |

| I <sub>sw(on)</sub> | switch-on current        |                                                  | _    | 12   | 40   | μA   |

#### Notes

1. The circuit is DC adjusted at V\_P = 6 to 18 V and  $\,$  C operating at V\_P = 8.5 to 18 V.

2. Only for BTL channel ( $V_{OUT4} - V_{OUT3}$ ).

### 13 AC CHARACTERISTICS

$V_P$  = 15 V;  $f_i$  = 1 kHz;  $T_{amb}$  = 25 °C; bandpa s 22 Hz o 22 kHz; measured according to Figs 6 and 7; unless otherwise specified.

| SYMBOL             | PARAMETER                       | CONDITIONS                                     | MIN. | TYP.        | MAX. | UNIT |  |  |

|--------------------|---------------------------------|------------------------------------------------|------|-------------|------|------|--|--|

| BTL chanr          | 3TL channel                     |                                                |      |             |      |      |  |  |

| Po                 | output power                    | $R_{L2} = 4 \Omega$ (see Fig.7); note 1        |      |             |      |      |  |  |

|                    |                                 | THD = 0.5%                                     | 16   | 20          | _    | W    |  |  |

|                    |                                 | THD = 10%                                      | 22   | 26          | _    | W    |  |  |

| THD                | total harm nic dist t n         | P <sub>o</sub> = 1 W                           | _    | 0.06        | -    | %    |  |  |

| B <sub>P</sub>     | power bandw dth                 | THD = 0.5%; $P_o = -1 dB$ with respect to 17 W | -    | 20 to 15000 | -    | Hz   |  |  |

| f <sub>ro(l)</sub> | low frequ ncy roll-off          | at –1 dB; note 2                               | _    | 25          | -    | Hz   |  |  |

| f <sub>ro(h)</sub> | high freq e y roll-off          | at –1 dB                                       | 20   | -           | -    | kHz  |  |  |

| G <sub>V</sub>     | closed loop voltage gain        |                                                | 25   | 26          | 27   | dB   |  |  |

| SVRR               | supply voltage ripple rejection | note 3;                                        |      |             |      |      |  |  |

|                    |                                 | operating                                      | 48   | -           | -    | dB   |  |  |

|                    |                                 | mute                                           | 46   | -           | _    | dB   |  |  |

|                    |                                 | standby                                        | 80   | -           | -    | dB   |  |  |

### TDA8512J

| SYMBOL             | PARAMETER                       | CONDITIONS                                     | MIN. | TYP. | MAX. |     |

|--------------------|---------------------------------|------------------------------------------------|------|------|------|-----|

| Z <sub>i</sub>     | input impedance                 |                                                | 25   | 30   | 38   | kΩ  |

| V <sub>n(o)</sub>  | noise output voltage            | operating; $R_s = 0 \Omega$ ; note 4           | -    | 70   | _    | μV  |

|                    |                                 | operating; $R_s = 10 \text{ k}\Omega$ ; note 4 | -    | 100  | 2 0  | μV  |

|                    |                                 | mute; notes 4 and 5                            | _    | 60   | -    | μV  |

| SE channe          | els                             | 1                                              |      |      | •    | •   |

| Po                 | output power                    | $R_{L1} = 2 \Omega$ (see Fig.7); note 1        |      |      |      |     |

|                    |                                 | THD = 0.5%                                     | 8.0  | 10   | -    | W   |

|                    |                                 | THD = 10%                                      | 11.  | 13.0 | -    | W   |

|                    |                                 | $R_{L1} = 4 \Omega$ (see Fig.7); note 1        |      |      |      |     |

|                    |                                 | THD = 0.5%                                     | _    | 5.5  | -    | w   |

|                    |                                 | THD = 10%                                      | -    | 7.0  | -    | W   |

| THD                | total harmonic distortion       | $P_o = 1 W$                                    | -    | 0.06 | -    | %   |

| f <sub>ro(I)</sub> | low frequency roll-off          | at –1 dB; note 2                               |      | 25   | -    | Hz  |

| f <sub>ro(h)</sub> | high frequency roll-off         | at –1 dB                                       | 20   | -    | -    | kHz |

| Gv                 | closed loop voltage gain        |                                                | 19   | 20   | 21   | dB  |

| SVRR               | supply voltage ripple rejection | note 3;                                        |      |      |      |     |

|                    |                                 | operating                                      | 48   | -    | -    | dB  |

|                    |                                 | mute                                           | 46   | _    | -    | dB  |

|                    |                                 | stan by                                        | 80   | _    | -    | dB  |

| Z <sub>i</sub>     | input impedance                 |                                                | 50   | 60   | 75   | kΩ  |

| V <sub>n(o)</sub>  | noise output voltage            | op rating R = 0 $\Omega$ ; note 4              | -    | 50   | _    | μV  |

|                    |                                 | operat g; $R_s = 10 \text{ k}\Omega$ ; note 4  | -    | 70   | 100  | μV  |

|                    |                                 | mute; notes 4 and 5                            | -    | 50   | -    | μV  |

| $\alpha_{cs}$      | channel separation              | $R_s = 1 k\Omega$                              | 40   | 60   | -    | dB  |

| $ \Delta G_V $     | channel unbalance               |                                                | _    | _    | 1    | dB  |

### Notes

- 1. Output power is measured di ectly a he output pins of the device.

- 2. Frequency response externally xed.

- 3. Ripple rejection measured at  $e o tput with a source impedance of 0 \Omega$ ; maximum ripple of 2 V (p-p) and at a frequency between 100 Hz t 10 kHz.

- 4. Noise measured in bandw dt of 20 Hz to 20 kHz.

- 5. Noise output voltage independant of  $R_s$  (V<sub>i</sub> = 0 V).

### TDA8512J

## 26 W BTL and $2 \times 13$ W SE or $4 \times 13$ W SE power amplifier

### 14 APPLICATION INFORMATION

### 14.1 Input configuration

- Inputs 1 and 2 are used for SE application on pin OUT1, respectively pin OUT2

- Input 3 can be configured for both SE and BTL application

- Input 4 can be used for SE application of pin OUT4, or for BTL application together with input 3. See Figs 6 and 7.

Note that the DC level of all input pins is half the supply voltage  $V_P$ , so coupling capacitors for the input pins are necessary!

Cut-off frequency for the input is:  $f_{i(co)} = 12$  Hz. Therefore it is not necessary to use high capacitor values on the input; so the delay during switch-on, which is necessary for charging the input capacitors, can be minimised. This results in a good low frequency response and good switch-on behaviour.

### 14.2 Output power

The output power versus supply voltage has been measured on the output pins of one channel, and at THD = 10%. The maximum output power is limited b the maximum supply voltage of 18 V and the ma imum available output current: 4 A repetitive peak curr nt.

### 14.3 Power dissipation

The power dissipation graphs are given for ne output channel in SE, respectively BTL application. So for total worst-case power dissipation the  $P_d$  of each ha nel must be added up.

### 14.4 Supply Voltage Ripple Re ection (SVRR)

The SVRR is measured with electr lytic capacitor of  $100 \ \mu$ F on pin RR and at a ban width  $10 \ Hz$  to  $80 \ k$ Hz, whereas the lowest frequeries c n be lower than  $10 \ Hz$ .

Proper supply bypassing s critical for low noise performance and hi h pow r supply rejection. The respective capacitor ocati should be as close to the device as possible and grounded to the power ground. A proper power supply d co pling also prevents oscillations. For suppressing higher frequency transients (spikes) on the supply line a capacitor with low ESR (typical 0.1  $\mu F$ ) has to be blaced as close as possible to the device. For suppressing lower frequency noise a d ripple signals, a large electrolytic capacitor (e.g.1000  $\mu F$  o more) must be placed close to the device

The bypass capacitor on the n RR du es the noise and ripple on the mid rail voltage. F good THD and noise performance, a low ESR capacitor recommended.

### 14.5 Switch-on and switch-of

To avoid audible plops du g switching on and switching off the supply voltage he pin MODE has to be set in standby condition (<2V) b fore the voltage is applied (switch-on) or removed (switch-off). Via the mute mode, the input- a d SVRR-capacitors are smoothly charged.

The turn on a d turn-off time can be influenced by an RC-c cuit on t e pin MODE (see Fig.3). Rapidly switching on and ff of the device or the pin MODE, may cause "click a pop" oise. This can be prevented by a proper timing on e pin MODE.

### 14.6 CB layout and grounding

r high system performance level certain grounding techniques are imperative. The input reference grounds have to be tied with their respective source grounds, and must have separate traces from the power ground traces; this will separate the large (output) signal currents from interfering with the small AC input signals. The small-signal ground traces should be physically located as far as possible from the power ground traces. Supply- and output-traces should be as wide as practical for delivering maximum output power. The PCB layout, which accommodates the TDA8510, TDA8511, and TDA8512 products, is shown in Fig.8.

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如 要下载或阅读全文,请访问: <u>https://d.book118.com/30810413103</u> 5006067