才

体

标

准

T/CESA XXXX—202X

# 半导体集成电路 串行 NOR 型快闪存储器测试方法

Semiconductor integrated circuits—Test methods of serial NOR Flash

202X-XX- XX 发布

202X-XX- XX 实施

# 目 次

| 前 | Ĵ    | 言IV                              |

|---|------|----------------------------------|

| 1 | 范围   | 5                                |

| 2 | 规范   | 性引用文件                            |

| 3 | 术语   | 和定义                              |

| 4 | 符号   | 和缩略语                             |

| 5 | 一般   | 要求                               |

| 6 | 功能   | 测试                               |

|   | 6.1  | 擦除操作功能测试                         |

|   | 6.2  | 页编程操作功能测试 8                      |

| 7 | 静态   | 参数测试                             |

|   | 7. 1 | 静态工作电流 I <sub>CCSB</sub> 8       |

|   | 7.2  | 关断电流 <i>I</i> <sub>CCPD</sub>    |

|   | 7.3  | 动态工作电流 $I_{\text{CCOP}}$         |

|   | 7.4  | 输出漏电流 I <sub>LO</sub> 11         |

|   | 7.5  | 输入漏电流 I <sub>LI</sub> 12         |

|   | 7.6  | 输入高电平电压 V <sub>II</sub>          |

|   | 7.7  | 输入低电平电压 $V_{\text{IL}}$          |

|   | 7.8  | 输出高电平电压 V <sub>OH</sub> 15       |

|   | 7.9  | 输出低电平电压 Vol 15                   |

| 8 | 动态   | 参数测试16                           |

|   | 8.1  | 串行时钟高脉宽时间 t <sub>CH</sub>        |

|   | 8.2  | 串行时钟低脉宽时间 tcl                    |

|   | 8.3  | 片选信号有效建立时间 tsl.CH18              |

|   | 8.4  | 片选信号有效保持时间 tchsh 19              |

|   | 8.5  | 片选信号失效建立时间 tshch 19              |

|   | 8.6  | 片选信号失效保持时间 tcHsL                 |

|   | 8.7  | 片选信号取消选择时间 tsHsL21               |

|   | 8.8  | 输出关断时间 <i>t</i> <sub>SHQ</sub> Z |

|   | 8.9  | 输出保持时间 tcLqx                     |

|   | 8 10 | 数据建立时间 <b>f</b> pvcH             |

| 8. 11 | 数据保持时间 <i>t</i> <sub>CHDX</sub>   | 23 |

|-------|-----------------------------------|----|

| 8. 12 | 输入保持建立时间 thlch                    | 24 |

| 8. 13 | 输入保持解除时间 thhch                    | 25 |

| 8. 14 | 输入保持持续时间 <i>tchhh</i>             | 26 |

| 8. 15 | 输入保持时间 <i>t<sub>CHHL</sub></i>    | 27 |

| 8. 16 | 输入保持生效到输出高阻延迟时间 tHLQZ             | 28 |

| 8. 17 | 输入保持解除到输出正常延迟时间 t <sub>HHQX</sub> | 28 |

| 8. 18 | 输入时钟到输出正常延迟时间 tcLQv               | 29 |

| 8. 19 | 写保护建立时间 <i>twHSL</i>              | 29 |

| 8.20  | 写保护保持时间 <i>t<sub>SHWL</sub></i>   | 30 |

| 8.21  | 状态寄存器写入周期时间 $t_W$                 | 31 |

| 8.22  | 页面编程时间 tpp                        | 31 |

| 8. 23 | 扇区擦除时间 tse                        | 32 |

| 8.24  | 央擦除时间 tBE                         | 32 |

| 8.25  | 片擦除时间 tCE                         | 33 |

| 附录 A  | (资料性) 测试图形说明                      | 35 |

| 附录 B  | (资料性) 真值表引脚说明                     | 37 |

| 参考文   | 7 献                               | 38 |

# 半导体集成电路 串行 NOR 型快闪存储器测试方法

#### 1 范围

本文件描述了半导体集成电路串行NOR型快闪存储器的功能、静态参数和动态参数测试的基本方法。

本文件适用于半导体集成电路领域中串行NOR型快闪存储器的功能、静态参数和动态参数的测试。

# 2 规范性引用文件

本文件没有规范性引用文件。

#### 3 术语和定义

下列术语和定义适用于本标准。

3. 1

# 访问时间 access time

地址或控制信号有效时到数据输出有效时的传输延迟时间。

3. 2

# 读周期时间 read cycle time

器件进行连续读操作时,地址变化的频率周期。

3.3

# 建立时间 setup time

地址或数据输入信号相较于控制信号有效沿提前输入到器件的时间。

3.4

# 保持时间 hold time

地址或数据输入信号在控制信号有效沿之后保持稳定的时间。

# 4 缩略语

CS#——chip select input, 芯片选择;

WP#——write protect input, 写保护;

DI——data input,数据输入;

DO——data output,数据输出;

CLK——serial clock input, 时钟输入;

HOLD——hold input,保持输入。

# 5 一般要求

# 5.1 测试环境要求

除另有规定外,推荐测试标准大气条件为:

- ——温度: 20℃~28℃;

- ——相对湿度: 40%~70%;

- ——气压: 86kPa~106kPa。

#### 5.2 测试注意事项

测试期间,应注意以下事项:

- a) 测试期间,应避免外界干扰对测试准确度的影响,测试设备引起的测试误差应符合器件产品技术要求的规定:

- b) 测试期间,施于被测器件的电源电压误差应在规定值的±1%以内,施于被测器件的其它电参量的准确度应符合器件产品技术要求的规定;

- c) 给器件加电前,应检查施加的电源电压和负载电流未超过被测器件产品技术要求的使用极限条件,不能接反电源电压极性;

- d) 被测器件与测试系统连接或断开时,不应超过器件的使用极限条件;

- e) 在静态参数测试和动态参数测试前,应进行功能测试;

- f) 测试期间,测试设备或操作者应避免因静电放电而引起器件失效。

#### 6 功能测试

#### 6.1 擦除操作功能测试

# 6.1.1 目的

验证器件从"0"擦除到"1"的操作,并读出。

# 6.1.2 测试原理

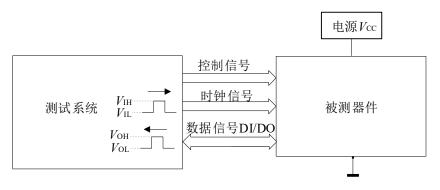

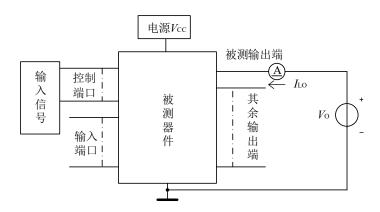

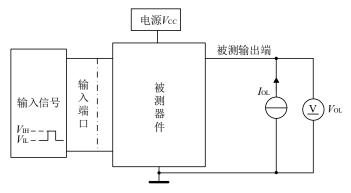

器件功能的测试原理图如图 1 所示。测试过程中,测试系统对器件提供输入信号,首先对控制信号脚、地址脚及数据输入脚输入相应写的指令及地址、数据,对存储单元进行擦除操作,之后对器件进行读"1"操作,通过测试系统的信号采集功能接收数据脚的输出信号。

图1 功能测试原理图

基本功能真值表如表1所示。

表1 功能真值表

|     | į     | 输出  | 模式  |    |    |    |

|-----|-------|-----|-----|----|----|----|

| CS# | HOLD# | WP# | CLK | DI | DO | 大人 |

| Н   | X     | X   | X   | X  | 三态 | 待机 |

| L   | L     | L   | CLK | 输入 | 输出 | 读取 |

|     | Į.    | 输出  | 模式  |    |    |    |

|-----|-------|-----|-----|----|----|----|

| CS# | HOLD# | WP# | CLK | DI | DO | 大人 |

| L   | L     | Н   | CLK | 输入 | 输出 | 写入 |

| L   | Н     | L   | CLK | 输入 | 保持 | 保持 |

注 1: H 为高电平, L 为低电平, X 为不关注, CLK 为时钟信号;

注 2: 引脚说明请参见附录 B。

注3: 适用于单路SPI模式,其他模式可参照相关文件规定。

# 6.1.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 ½;

- b) 相应输入端施加的高低电平  $V_{\text{II}}/V_{\text{IL}}$ 、时钟频率 f、不同脉冲相互间的时间关系;

- c)输出比较电平 Vot/Vot 和输出负载条件。

# 6.1.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压 Vcc;

- c) 输入高低电平与输出负载条件按器件产品技术要求给定;

- d) 参照表 2 将控制端口给定相应的信号,输入写使能和擦除操作的指令,并从输入端口输入指定的地址信号,对该地址所在存储空间进行擦除操作;

- e) 参照表 2 将控制端口给定相应的信号,输入读操作的指令,输入端口输入相应的地址信号,在输出端口进行采样,验证读出的数据是否为全"1",若是全"1",则表示器件擦除功能正常,若读出的数据非全"1",则需分别对擦写和读操作进行分析,确认器件是否存在擦写或读操作故障,功能测试参照表 2 示例的指令集。

表 2 功能指令集

| INSTRUCTIO    | ON NAME | BYTE1 | BYTE2   | вутез               | BYTE4   | BYTE5   | ВҮТЕ6   |

|---------------|---------|-------|---------|---------------------|---------|---------|---------|

| CLOCK NUMBER  | 时钟数     | (0-7) | (8-15)  | (16–23)             | (24-31) | (32–39) | (40-47) |

| Write Enable  | 写使能     | 06h   |         |                     |         |         |         |

| Write Disable | 禁止写入    | 04h   |         |                     |         |         |         |

| Read Status   | 读取状态寄   | 05h   | (S7-S0) |                     |         |         |         |

| Register      | 存器      | 0511  | (37-30) |                     |         |         |         |

| Write Status  | 写入状态寄   | 01h   | (S7-S0) | (S15-S8)            |         |         |         |

| Register      | 存器      | OIII  | (37 30) | (313-30)            |         |         |         |

| Page Program  | 页编程     | 02h   | A23-A16 | A15-A8              | A7-A0   | D7-D0   | D7-D0   |

| Sector        | 扇区擦除    | 20h   | A23-A16 | A15-A8              | A7-A0   |         |         |

| Erase (4K)    | 网区徐陈    | 2011  | A25-A10 | A15 <sup>-</sup> A6 | A7-A0   |         |         |

| Block         | 块擦除     | 52h   | A23-A16 | A15-A8              | A7-A0   |         |         |

| Erase (32K)   | 大1余 休   | 9211  | A23-A10 | A15 <sup>-</sup> A0 | A1 AU   |         |         |

| Block<br>Erase(64K)   | 块擦除  | D8h     | A23-A16 | A15-A8 | A7-A0 |           |         |

|-----------------------|------|---------|---------|--------|-------|-----------|---------|

| Chip Erase 芯片擦除       |      | C7h/60h |         |        |       |           |         |

| Power-down            | 断电   | B9h     |         |        |       |           |         |

| Read Data             | 读出数据 | 03h     | A23-A16 | A15-A8 | A7-A0 | (D7-D0)   |         |

| Fast Read             | 快速读取 | 0Bh     | A23-A16 | A15-A8 | A7-A0 | dummy     | (D7-D0) |

| Release<br>Power-down | 解除断电 | ABh     | dummy   | dummy  | dummy | (ID7-ID0) |         |

#### 6.2 页编程操作功能测试

# 6.2.1 目的

验证器件从"1"页编程到"0"的操作,并读出。

# 6.2.2 测试原理

器件功能的测试原理图如图1所示。测试过程中,测试系统对器件提供输入信号,首先对控制信号脚、地址脚及数据输入脚输入相应写的指令及地址、数据,对存储单元进行页编程操作,之后对器件进行读操作,通过测试系统的信号采集功能接收数据脚的输出信号。基本功能真值表如表1所示。

# 6.2.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压  $V_{CC}$ ;

- b) 相应输入端施加的高低电平  $V_{IH}/V_{IL}$ 、时钟频率 f、不同脉冲相互间的时间关系;

- c)输出比较电平 VoH/VoL 和输出负载条件。

# 6.2.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c) 输入高低电平与输出负载条件按器件产品技术要求给定;

- d) 参照表 2 将控制端口给定相应的信号,输入写使能和页编程的指令,并从输入端口输入指定的地址信号,将目标数据通过数据端口写入到该地址中;

- e)参照表 2 将控制端口给定相应的信号,输入读操作的指令,输入端口输入相应的地址信号,在输出端口进行采样,验证读出的数据是否和上一步写入的目标数据相同,若相同,则表示器件读写功能正常,若读出的数据不同,则需分别对写和读操作进行分析,确认是否是器件本身故障,功能测试参照表 2 示例的指令集。

# 7 静态参数测试

# 7.1 静态工作电流 I<sub>CCSB</sub>

# 7.1.1 目的

测试 TTL 电平下器件的静态工作电流。

# 7.1.2 测试原理

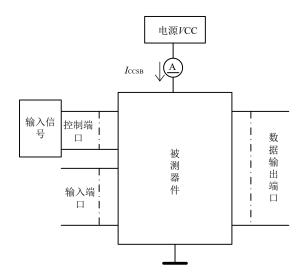

$I_{\text{CCSB}}$ 的测试原理图如图 2 所示。测试过程中,通过对控制端口输入指定的信号,输入端口的状态可不关注,将器件置于待机状态,测量此时流过电源端的电流。

图2 静态工作电流 /ccs测试原理图

# 7.1.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 *V*<sub>CC</sub>;

- b)输入信号条件,片选信号输入高电平信号  $V_{\rm IH}$ ;

- c) 输出负载条件。

# 7.1.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中:

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c)输入条件按照器件产品技术要求给定,片选信号使能端口施加器件产品技术要求规定的搞电平 (一般为 V<sub>CC</sub>);

- d) 按照表 1 将控制端口置于相应状态, 使被测器件处于待机工作状态;

- e)测量流过电源端  $V_{CC}$  的电流,即静态工作电流  $I_{CCSB}$ ,记录测试值;

# 7.2 关断电流 I<sub>CCPD</sub>

# 7.2.1 目的

测试器件的关断电流。

# 7.2.2 测试原理

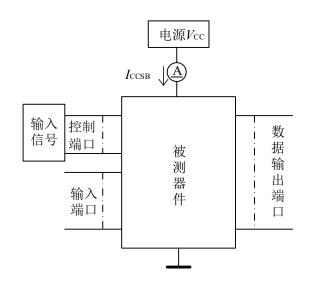

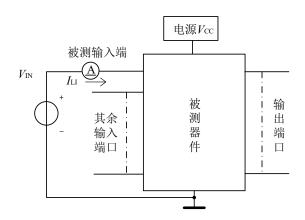

$I_{CCPD}$  的测试原理图如图 3 所示。测试过程中,通过对控制端口输入指定的信号,输入端口输入指定的信号,将器件置于关机状态,测量此时流过电源端的电流。

图3 静态工作电流Iccsn测试原理图

# 7.2.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 *V*<sub>CC</sub>;

- b) 输入信号条件;

- c) 输出负载条件。

# 7.2.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c)输入条件按照器件产品技术要求给定,片选信号使能端口施加器件产品技术要求规定的高电平  $(-\text{般为 V}_{CC})$ ;

- d) 按照表 2, 输入断电指令, 使被测器件处于断电状态;

- e)测量流过电源端  $V_{\rm CC}$  的电流,即为关断电流  $I_{\rm CCPD}$ ,记录测试值;

# 7.3 动态工作电流 Iccop

# 7.3.1 目的

测试器件分别处于只读、写状态寄存器、页编程、扇区擦除、块擦除和芯片擦除工作状态下的动态工作电流。

# 7.3.2 测试原理

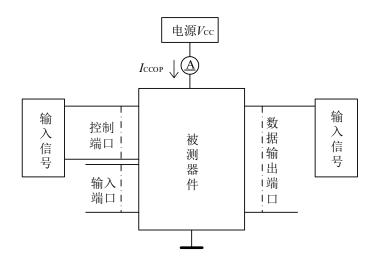

$I_{CCOP}$  的测试原理图如图 4 所示。测试过程中,对器件的输入端口给定指定的信号,并以一定的时钟周期对器件进行访问,输出端口不关注,测量此时流过电源端口的电流。

图4 动态工作电流Iccop测试原理图(输入端口要给信号)

# 7.3.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 *V*<sub>CC</sub>;

- b) 输入高低电平条件 V<sub>IH</sub>/V<sub>IL</sub> 和输出负载条件;

- c)工作频率 f。

# 7.3.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加器件产品技术要求规定的电压值 Vcc:

- c) 输入端条件施加器件产品技术要求规定的电平;

- d)参照表 1 和表 2 给定输入信号,采用器件产品技术要求规定的工作频率对器件进行读写操作;

- e) 在器件处于正常工作状态时,测量流过电源端  $V_{\rm CC}$  的电流即为动态工作电流  $I_{\rm CCOP}$ , 记录测试值;

# 7.4 输出漏电流 ILO

# 7.4.1 目的

测试器件处于三态时输出端的漏电流。

# 7.4.2 测试原理

I<sub>0</sub> 的测试原理图如图 5 所示。测试过程中,对器件控制端口输入相应的信号,使输出端口处于三态状态,并对被测输出端口施加相应电压 I<sub>6</sub>,测量此时流过该输出端口的电流。

图5 输出漏电流ILO测试原理图

# 7.4.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 *V*<sub>CC</sub>;

- b) 输入高低电平条件 V<sub>IH</sub>/V<sub>IL</sub> 和输出负载条件;

- c)输出端施加电压 $V_0$ 。

# 7.4.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c) 参照表 1,输入端施加器件产品技术要求规定的逻辑电平,使器件输出端处于三态状态;

- d)被测输出端施加器件产品技术要求规定的输出电压  $V_{\rm O}$ (一般为 0V 和  $V_{\rm CC}$  两种条件);

- e) 在被测输出端测得电流即为输出漏电流 ILO, 记录测试值。

# 7.5 输入漏电流 ILI

# 7.5.1 目的

测试器件输入端口的漏电流。

# 7.5.2 测试原理

$I_{\square}$ 的测试原理图如图 6 所示。测试过程中,对器件被测输入端口施加相应电压  $V_{\square}$ ,测量此时流过该输入端口的电流。

图6 输入漏电流 / 测试原理图

# 7.5.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 ½;

- b)输入端施加的电压 V<sub>IN</sub>。

# 7.5.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{\text{CC}}$ ;

- c) 被测输入端施加器件产品技术要求规定的输入电压  $V_{\rm IN}$  (一般为 0V 和  $V_{\rm CC}$  两种条件);

- d) 在被测输入端测得输入电流即为输入漏电流 Iu. 记录测试值。

# 7.6 输入高电平电压 Уш

# 7.6.1 目的

测试能使器件正常工作的最小输入高电平电压。

# 7.6.2 测试原理

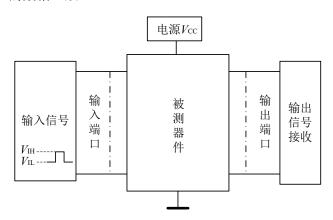

$V_{\text{H}}$ 的测试原理图如图 7 所示。测试过程中,测试系统对器件提供的逻辑高电平输入电压设置为  $V_{\text{H}}$ 、逻辑低电平电压  $V_{\text{L}}$  设为 0V,对器件存储单元进行写操作,之后进行读操作,采集输出端口的输出信号,验证输出数据是否和写入的数据一致。

# 图7 输入高低电平电压 /////测试原理图

# 7.6.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 1/cc;

- b) 相应输入端施加的高低电平  $V_{\text{II}}/V_{\text{II}}$ 、时钟频率 f、不同脉冲相互间的时间关系;

- c)输出比较电平 //// 和输出负载条件。

# 7.6.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c) 非被测输入端施加器件产品技术要求规定的条件, 非被测输出端开路;

- d)被测输入端输入的高电平  $V_{\rm IH}$  从  $V_{\rm CC}$  值开始降低,找到能使输出端输出电压为规范规定的电压值时的最小输入电压,该输入电压即为最小输入高电平电压  $V_{\rm IH}$  ,记录该测试值;

- e) 按照以上步骤,针对每个被测输入端分别进行测试。

# 7.7 输入低电平电压 $V_{\rm IL}$

#### 7.7.1 目的

测试能使器件正常工作的最大输入低电平电压。

#### 7.7.2 测试原理

$V_{\text{LI}}$  的测试原理图如图 7 所示。测试过程中,测试系统对器件提供的逻辑高电平输入电压  $V_{\text{LI}}$ 与  $V_{\text{CI}}$  保持一致、逻辑低电平电压设置为  $V_{\text{LI}}$ ,对器件存储单元进行写操作,之后进行读操作,采集输出端口的输出信号,验证输出数据是否和写入的数据一致。

# 7.7.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 Vcc;

- b) 相应输入端施加的高低电平 V<sub>III</sub>/ V<sub>II</sub>、时钟频率 f、不同脉冲相互间的时间关系;

- c)输出比较电平 Vot/Vot 和输出负载条件。

# 7.7.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中。

- b) 电源端施加规定的电压  $V_{\rm CC}$ 。

- c) 非被测输入端施加器件产品技术要求规定的条件, 非被测输出端开路。

- e) 按照以上步骤,针对每个被测输入端分别进行测试。

# 7.8 输出高电平电压 VoH

# 7.8.1 目的

测试器件输出端口输出为逻辑高电平时的输出电压。

#### 7.8.2 测试原理

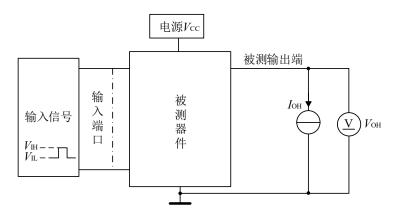

$V_{01}$ 的测试原理图如图 8 所示。测试过程中,先对器件的存储单元进行擦除操作,之后对器件进行读"1"操作,使输出端口处于高电平状态,并对被测输出端口施加相应的负载电流  $I_{01}$ ,测量此时被测输出端口的电压。

图8 输出高电平电压VoH测试原理图

# 7.8.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 Vcc;

- b) 相应输入端施加的高低电平  $V_{\text{II}}/V_{\text{II}}$ 、时钟频率 f、不同脉冲相互间的时间关系;

- c)输出负载电流 IoH。

# 7.8.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加器件产品技术要求规定的电压  $V_{CC}$ ;

- c) 输入端施加器件产品技术要求规定的条件;

- d)参照表 2 指令,对器件存储阵列进行擦除操作;

- e) 对器件进行读操作,被测输出端口输出电压为高电平时,对被测输出端口施加器件产品技术要求规定的负载电流 *I*<sub>OH</sub>;

- f) 在被测输出端测得输出高电平电压即为 VoH, 记录测试值。

# 7.9 输出低电平电压 $V_{\rm OL}$

#### 7.9.1 目的

测试器件输出端口输出为逻辑低电平时的输出电压。

# 7.9.2 测试原理

$V_{01}$ 的测试原理图如图 9 所示。测试过程中,先对器件的存储单元进行写全"0",之后对器件进行 读操作,使输出端口处于低电平状态,并对被测输出端口施加相应的负载电流  $I_{01}$ ,测量此时被测输出端口的电压。

图9 输出低电平电压 6.测试原理图

# 7.9.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 ½c;

- b) 相应输入端施加的高低电平  $V_{\text{II}}/V_{\text{II}}$ 、时钟频率 f、不同脉冲相互间的时间关系;

- c) 输出负载电流 Io.。

# 7.9.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加器件产品技术要求规定的电压  $V_{CC}$ ;

- c) 输入端施加器件产品技术要求规定的条件;

- d) 参照表 2 指令,对器件存储阵列进行写全"0"操作;

- e) 对器件进行读操作,被测输出端口输出电压为低电平时,对被测输出端口施加器件产品技术要求规定的负载电流 *IoL*;

- f) 在被测输出端测得输出电压即为输出低电平电压 Vol., 记录测试值。

# 8 动态参数测试

# 8.1 串行时钟高脉宽时间 tcH

#### 8.1.1 目的

测试器件进行正常工作时的最小时钟高脉宽时间。

# 8.1.2 测试原理

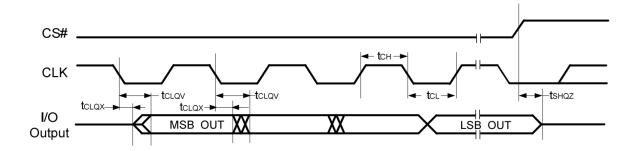

$t_{\text{CH}}$ 的测试原理图如图 1 所示,波形图如图 10 所示。测试过程中,对器件存储单元进行读操作,时钟信号的高电平脉宽为  $t_{\text{CH}}$ 。

图10 串行输出波形图

# 8.1.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压  $V_{CC}$ ;

- b)输入脉冲高低电平 $V_{\rm IH}/V_{\rm IL}$ 、脉冲幅度、脉冲上升/下降时间 $t_{\rm r}/t_{\rm f}$ 、时钟频率f、不同脉冲相互间的时间关系;

- c)输出比较电平 VoH/VoL和输出负载条件。

# 8.1.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c) 输入条件与输出负载条件按器件产品技术要求给定;

- d) 输入脉冲条件按照器件产品技术要求给定:

- e)将特定数据(建议使用棋盘码)写入全部存储单元中,按照器件产品技术要求规定的时钟频率 读出数据,验证读写操作是否正确;

- f) 以一定步进将读操作的时钟高脉宽不断缩小,每步进一次测试一遍读操作,验证读出数据是否正确,直至找到能使器件正确读出时的最小时钟高脉宽时间,即为串行时钟高脉宽时间  $t_{\text{CH}}$ , 记录该测试值。

# 8.2 串行时钟低脉宽时间 $t_{\rm CL}$

# 8.2.1 目的

测试器件进行正常工作时的最小时钟低脉宽时间。

# 8.2.2 测试原理

$t_{\rm CL}$ 的测试原理图如图 1 所示,波形图如图 10 所示。测试过程中,对器件存储单元进行读操作,时钟信号的低电平脉宽为  $t_{\rm CL}$ 。

# 8.2.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 Vcc;

- b)输入脉冲高低电平  $V_{\rm IH}/V_{\rm IL}$ 、脉冲幅度、脉冲上升/下降时间  $t_{\rm r}/t_{\rm f}$ 、时钟频率 f、不同脉冲相互间的时间关系:

- c)输出比较电平 VoH/VoL和输出负载条件。

# 8.2.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压 ½;

- c) 输入条件与输出负载条件按器件产品技术要求给定;

- d) 输入脉冲条件按照器件产品技术要求给定;

- e) 将特定数据(建议使用棋盘码)写入全部存储单元中,按照器件产品技术要求规定的时钟频率 读出数据,验证读写操作是否正确;

- f) 以一定步进将读操作的时钟低脉宽不断缩小,每步进一次测试一遍读操作,验证读出数据是否正确,直至找到能使器件正确读出时的最小时钟低脉宽时间,即为串行时钟低脉宽时间  $t_{CL}$ ,记录该测试值。

# 8.3 片选信号有效建立时间 tSLCH

# 8.3.1 目的

测试器件由片选信号控制写操作时片选信号有效沿到第一个时钟输入的时间。

# 8.3.2 测试原理

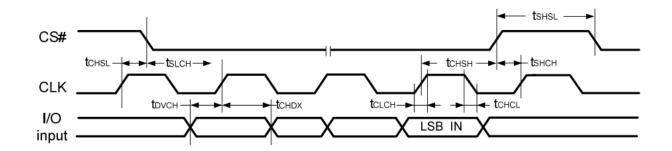

$t_{SLCH}$ 的测试原理图如图 1 所示,波形图如图 11 所示。测试过程中,对器件进行写操作时,由片选信号下降沿来控制数据输入有效,测量片选信号下降沿到第一个时钟输入上升沿的时间。

图11 串行输入波形图

# 8.3.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压 *Vcc*;

- b)输入脉冲高低电平  $V_{\rm IH}/V_{\rm IL}$ 、脉冲幅度、脉冲上升/下降时间  $t_{\rm r}/t_{\rm f}$ 、时钟频率 f、不同脉冲相互间的时间关系;

c)输出比较电平 VoH/VoL 和输出负载条件。

# 8.3.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压 Vcc;

- c) 输入条件与输出负载条件按器件产品技术要求给定;

- d)被测片选信号输入端施加器件产品技术要求规定的脉冲,对器件输入读操作指令;

- e) 片选信号下降沿到第一个时钟输入上升沿时间按照规范给定的值来设定,验证读操作数据是否 正确写入;

- f) 以一定步进将片选信号下降沿到第一个时钟输入上升沿的时间间隔不断减小,通过正常读操作 验证数据正确读出的最小时间间隔,即得到片选信号有效建立时间 *tsum*,记录该测试值。

#### 8.4 片选信号有效保持时间 t<sub>CHSH</sub>

#### 8.4.1 目的

测试器件由片选信号控制写操作时最后一个时钟输入信号到片选信号无效的时间。

# 8.4.2 测试原理

*tcussi*的测试原理图如图 1 所示,波形图如图 11 所示。测试过程中,对器件进行写操作时,由片选信号上升沿来控制数据输入无效,测量最后一个时钟输入信号上升沿到片选信号上升沿的时间。

# 8.4.3 测试条件

测试期间,应规定以下测试条件:

- a) 电源电压  $V_{CC}$ ;

- b)输入脉冲高低电平 $V_{\rm IH}/V_{\rm IL}$ 、脉冲幅度、脉冲上升/下降时间 $t_{\rm r}/t_{\rm f}$ 、时钟频率f、不同脉冲相互间的时间关系:

- c)输出比较电平 VoH/VoL 和输出负载条件。

# 8.4.4 测试程序

测试程序如下:

- a) 在规定的环境条件下,将被测器件接入测试系统中;

- b) 电源端施加规定的电压  $V_{CC}$ ;

- c) 输入条件与输出负载条件按器件产品技术要求给定;

- d)被测片选信号输入端施加器件产品技术要求规定的脉冲,其余控制输入端的有效信号优先于片选信号的有效信号给出,对器件进行写使能和页编程;

- e) 写使能和写操作结束时,最后一个时钟输入信号上升沿到片选信号上升沿的时间按照规范给定的值来设定,通过正常读写操作验证数据是否正确写入:

- f) 以一定步进将最后一个时钟输入信号上升沿到片选信号上升沿的时间间隔不断减小,通过正常 读操作验证数据正确写入的最小时间间隔,即为片选信号有效保持时间 *tcHSH*,记录该测试值。

# 8.5 片选信号失效建立时间 tshch

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如要下载或阅读全文,请访问: <a href="https://d.book118.com/58524220332">https://d.book118.com/58524220332</a> 3011313